Researchers at Khalifa University’s System-on-Chip Lab have filed a patent for a novel low-cost glucose sensor that can measure glucose at neutral pH conditions, resulting in a lower-cost and more compact device.

A research group led by Dr. Heba Abunahla, Postdoctoral Fellow of Electrical Computer Engineering at KU’s System-on-Chip Lab (SoCL), has developed a novel low-cost non-enzymatic glucose sensor for adults. While glucose sensors are not revolutionary in themselves, the distinguishing property of this sensor is its ability to measure glucose at neutral pH conditions. The sensor is the result of a cooperative effort with faculty from the departments of Chemistry (Dr. Maguy Abi Jaoude), Mechanical Engineering (Dr. Anas Alazzam), and Electrical Engineering and Computer Science (Dr. Mahmoud Al-Qutayri and Dr. Baker Mohammad).

Read full story here: https://www.ku.ac.ae/portable-glucose-sensor-could-improve-diabetes-treatment

Computer scientists have long been inspired by the human brain, aiming to design a computer that is able to store, retrieve and process information just as efficiently as the brain. The memristor, short for memory resistor, could be the key to designing such a computer as it processes information in a way that mimics the brain’s synapses and enables efficient neural network architecture.

A team from Khalifa University has now developed a new type of flexible memristor device, called ‘NeuroMem’, that will extend the application of memristors to flexible electronic technologies like wearable smart devices. The team, including Dr. Baker Mohammad, Associate Professor of Electrical Engineering and Computer Science and Director of the System-on-Chip Lab (SoCL), Dr. Heba Abunahla, Research Scientist, Dr. Yasmin Halawani, Postdoctoral fellow, and Dr. Anas Alazzam, Associate Professor of Mechanical Engineering, published their findings recently in Scientific Reports.

Read full story here: https://www.ku.ac.ae/neuromem-mimicking-the-synapses-in-the-human-brain

A team of researchers from Khalifa University has investigated a memristor-based image compression architecture to speed up image compression while also making the devices using this technology much smaller and more energy efficient.

The team comprised Dr. Yasmin Halawani, Post-doctoral Researcher, Dr. Baker Mohammad, Associate Professor, Dr. Mahmoud Al-Qutayri, Professor, all from the System-on-Chip Lab and Department of Electrical and Computer Engineering at Khalifa University, and Dr. Said Al-Sarawi from the Center for Biomedical Engineering at the University of Adelaide, Australia.

Dr. Halawani explained in her doctoral thesis that today’s devices are “jam-packed with a variety of sensors, which are collectively expected to generate more than 40 zettabytes in 2020.” That’s one billion terabytes of data or one trillion gigabytes.

“This huge amount of generated data needs to be processed at a fast rate using complex algorithms to interpret the information,” explained Dr. Halawani. “This is computationally demanding, but Internet-of-Things devices tend to be energy-constrained and have limited resources, so innovative architectures and technologies that enable efficient.

Read full story here: https://www.ku.ac.ae/shrinking-images-for-efficient-transfer-and-storage-with-memristors

The growth of wireless communication technologies that are integral to the Fourth Industrial Revolution, or Industry 4.0, has necessitated the development of cost- and power-efficient devices that can tune and filter the radiofrequency (RF) spectrum used in advanced wireless systems.

A collaborative research project has, for the first time, demonstrated the feasibility of a next-generation RF tuning device to allow cost-effective and power-efficient adaptable communication systems. The project is led by Dr. Heba Abunahla, Research Scientist at Khalifa University (KU), and is part of KU’s System-on-a-Chip Lab, which is dedicated to the design and realization of advanced electronic circuits and systems and sensory devices.

The wireless technologies that modern society uses for many daily activities, like mobile phones and fitness trackers, and that are critical for the growth of the Internet of Things (IoT), transmit data by manipulating radio waves. They do this through tiny specialized sensors, known as RF filters, that send and receive data. As wireless communication has grown, the radio bandwidths used to transmit this data have become more and more crowded. This has necessitated the development of robust RF filters that can automatically and intelligently tune the bandwidth to remove unwanted radio signals – a type of filter known as tunable RF filters.

“Being a crucial component in radio frequency transceivers, filters play a major role in wireless communication, which is among the main pillars of the IoT technology stack. The main purpose of our project was to demonstrate experimentally, after verifying the design with simulations, the feasibility to integrate a new, emerging memory device within the metal of the RF filter to achieve frequency tuning,” Dr. Abunahla explained.

The collaborative group includes System-on-a-Chip Lab Director Dr. Baker Mohammad, Dr. Rida Gadhafi of the University of Dubai, and Dr. Mihai Sanduleanu, Dr. Anas Alazzam, and Mamady Kebe from KU. A paper on their research was recently published in the peer-reviewed, open-access journal Scientific Reports – Nature.

Their project integrates tunable RF filters with the emerging technology of memristor, an electrical component that “remembers” the amount of charge that has previously flowed through it and adjusts its resistance accordingly. Memristor devices are able to retain the data stored within them without the need for a power source. When memristors are used to store data they are referred to as resistive random access memory (RRAM) devices.

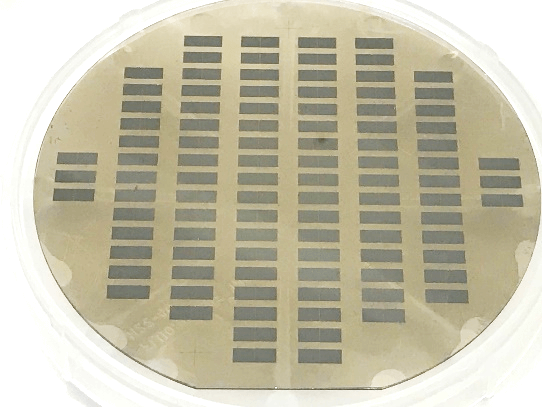

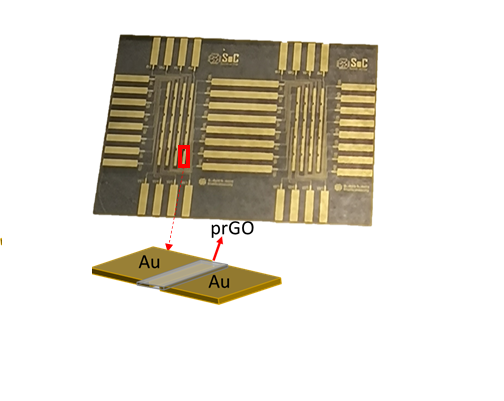

Dr. Abunahla’s team proposed constructing an RRAM device using graphene oxide – a chemically modified version of the “wonder material” graphene – and integrating it into the metal of the RF filter. Graphene oxide shares some of graphene’s noted strength, but is far cheaper and easier to use. Although initially not as conductive as graphene, methods have been developed to enhance graphene oxide’s transparency and conductance.

“Graphene-based switching devices are gaining great interest due to their excellent properties in terms of low cost, flexibility, adaptability, and being environmentally friendly. Deploying graphene as electrodes in RRAM devices can increase its conductivity and thus improve the device’s performance,” said Dr. Abunahla.

The team first tested their hypothesis by designing a detailed computer simulation. To provide a proof of concept, they then developed a prototype tunable RF filter using graphene oxide. While previous research projects have used RRAM as a standalone component to tune resistance, the team integrated the graphene oxidebased RRAM into the metal of the RF filter.

To demonstrate the diversity of the resulting tunable RF filter, the team tested their proposed device design using three different metals – copper, gold, and silver – for its electrodes. All three metals demonstrated the potential to be deployed in the tunable RF filter depending on the intended use of the communication element. The proof-of-concept device used gold to demonstrate the proposed RRAM-based filter tuning. Testing of the prototype device at room temperature for two hours, in both the on and off position, demonstrated that the device was stable and could hold its last written state for up to one year.

“This project proved the possibility of tuning RF devices using a cost-efficient and power-effective approach. The results exhibited by this project showed promising insights that serve as milestones in the research of memory-based adaptable communication systems,” Dr. Abunahla said.

The research team asserted that their project has significant potential for commercialization in the local and global telecom markets. The RF tunable filter market was estimated to be worth $89 million in 2020, and is expected to reach $148 million by 2025, according to research published by MarketsandMarkets.

“Our device enables low-cost and low-power tunable filters for alwaysconnected devices, which is an important contribution to the UAE’s Fourth Industrial Revolution, where we foresee large-scale adoption of IoT and artificial intelligenceenabled technologies and systems,” Dr. Abunahla explained.

The Fourth Industrial Revolution – or Industry 4.0 – is the ongoing automation of manufacturing and industry through smart technologies like IoT and machine-tomachine communications. Under the Strategy for the Fourth Industrial Revolution, launched in 2017, the UAE is looking to become an Industry 4.0 hub to increase its contribution to the national economy by advancing innovation and future technologies.

The next step for the project is to enhance the filter design to adapt to the fifth-generation technology standard for broadband cellular networks, known as 5G. 5G networks, which were introduced in 2019, have greater bandwidth than previous cell networks. This increased bandwidth enables higher download speeds, which in turn supports more rapid communication, business, and the integration of smart technologies.

This article was originally published in the UAE Ministry of Education’s research magazine, Innovation@UAE, and can be found here: https://issuu.com/moeuae/docs/explorer_6384_research_magazine_en_final_dps

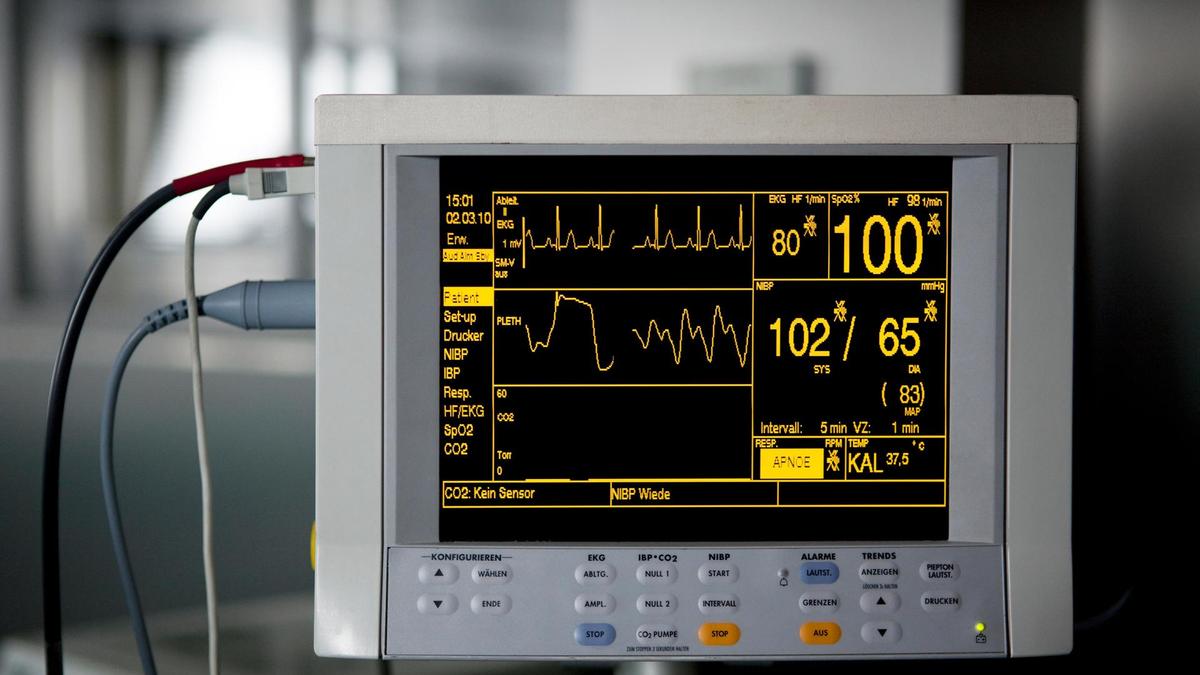

Vital signs such as blood pressure and heart rate could soon be monitored wirelessly via radar following pioneering work by UAE researchers.

A team at Khalifa University believe the technology could be used in hospitals and from homes, reducing the need for doctors’ house visits and avoiding the need for patients to be physically hooked up to machines.

Scientists hope that in time the radars could also be deployed in public settings such as airports to monitor the health of passengers and prevent the spread of future pandemics.

Read full story here: https://www.thenationalnews.com/uae/health/pioneering-uae-research-monitors-vital-signs-by-radar-1.1002005

A team of researchers from Khalifa University has developed a portable Covid-19 testing kit, no larger than your average smartphone. The new kit is both portable and can deliver the results in 45 minutes only.

Dr. Anas Alazzam, Associate Professor of Mechanical Engineering and member of the System on Chip Center (SOCC) is the primary investigator for the project with Dr. Habiba AlSafar, Director of the Khalifa University Center for Biotechnology and Associate Professor of Genetics and Molecular Biology, as co-principal investigator. The research team includes the Postdoctoral Researchers Dr. Waqas Waheed and Dr. Sueda Saylan, along with Research Associate Hussein Kannout.

Read full story here: https://www.ku.ac.ae/khalifa-university-research-team-develops-new-portable-cost-effective-pcr-test-to-help-detect-covid-19-in-45-minutes

A science paper written by researchers from Khalifa University’s System on Chip Center (SoCC) received 1,800 article downloads in 2020, placing it as one of the top 100 downloaded materials science papers for Scientific Reports in 2020. Their paper describes a new type of flexible memristor device, that could extend the application of memristors to flexible electronic technologies like wearable smart devices. Scientific Reports published more than 650 materials science papers in 2020, and so a position in the top 100 most downloaded articles is an extraordinary achievement, showing that KU’s science is of real value to the research community!

Find out about their research paper here.

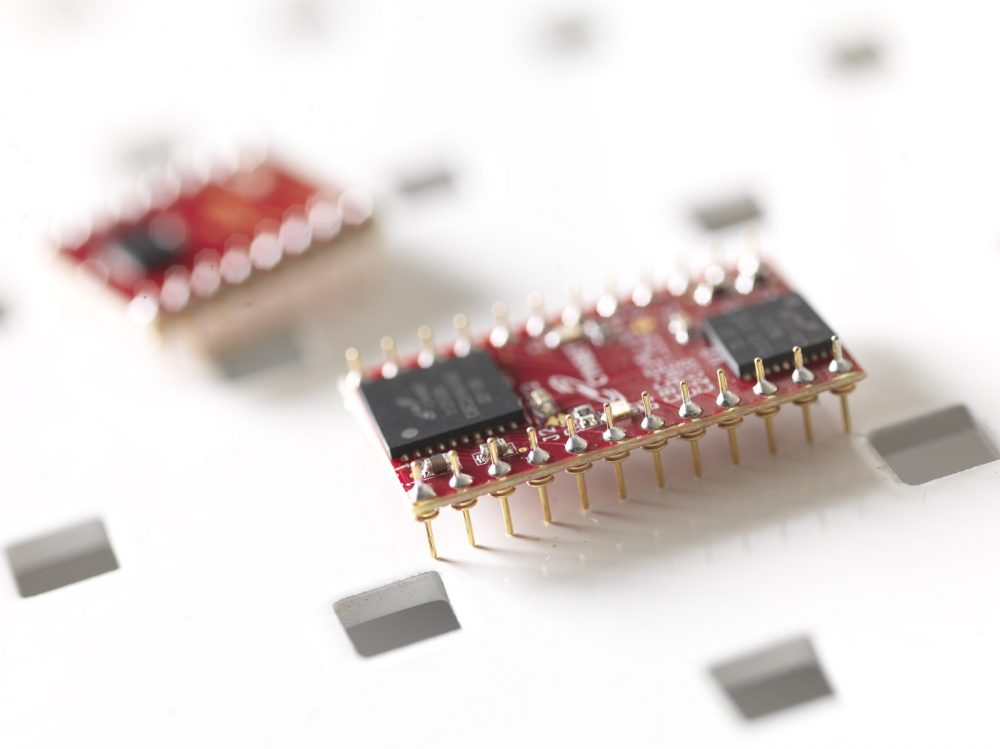

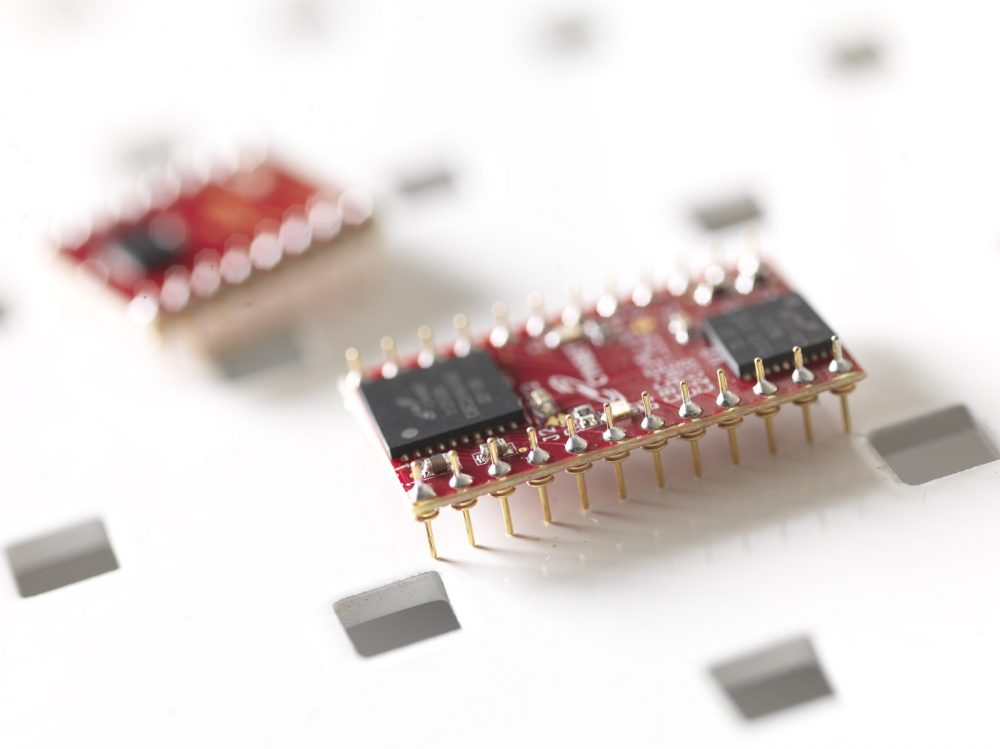

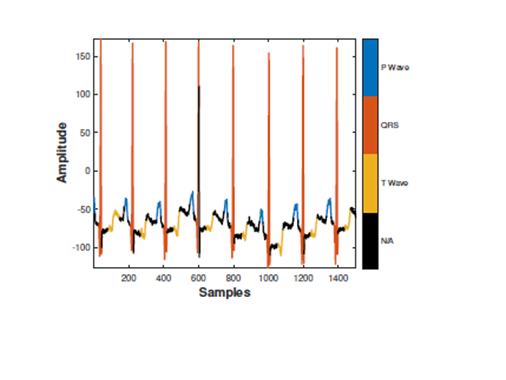

The electrocardiogram signal (ECG), a record of electrical activity of the cardiac muscle, has been used in diagnosing many cardiopathies. Wearable devices equipped with readout sensors and circuits can be used to record and process weak ECG signals. In this paper, a pre-trained neural network was implemented for detecting the QRS feature of an ECG signal, which is crucial for auto-diagnostic of various cardiopathies. To take advantage of the fast evolution of artificial intelligence and its ability to find non-linear relationships, neural network based feature extraction of ECG signals for wearable devices was explored and tested using ASIC implementation flow. Firstly, a high-level simulation was carried out in MATLAB and verified with test data obtained from PhysioNET database. Recurrent neural network (RNN) MLP was created and trained using the data obtained from PhysioNET database. A high-level performance evaluation was carried out using the same network for P and T wave extraction. The weight and bias matrices obtained from the high-level trained network in MATLAB were used in the design of the hardware. An accuracy of 96.55% was achieved in the hardware implementation of the network.

View paper and presentation: https://ieeexplore-ieee-org.libconnect.ku.ac.ae/document/9180703/metrics#metrics

This paper presents a novel analog resistive random-access memory (RRAM), named NeuroMem, which consists of Au/GO/Au. The device’s resistance can be tuned to any value within its R OFF to R ON range with high precision. The analog characteristic of NeuroMem mimics the memorization behavior of the brain, which makes it great asset for artificial neural network applications. In this work, NeuroMem-based crossbars are fabricated to hold the synaptic weights needed to perform Iris classification. The weight values are mapped to conductance states within NeuroMem R OFF to R ON range, and then written accurately on the actual devices. Unlike other RRAM-based hardware with limited conductance states, in this work no quantization is needed which enables efficient in memory-computing without scarifying accuracy. Furthermore, NeuroNem device has been demonstrated in crossbars on flexible polymer substrate using standard photolithography process, which facilitates producing low cost flexible electronics. This work opens up great insights towards realizing RRAM-based computing at the edge.

View full paper here: https://ieeexplore.ieee.org/document/9184484

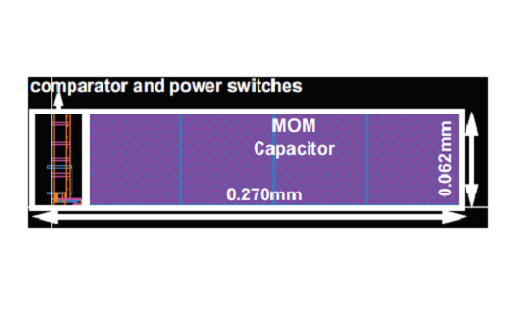

This paper presents a fast and an efficient digital LDO (DLDO) regulator utilizing a clock-less ratioed logic comparator (RLC). In addition to eliminating the clock, the proposed RLC-DLDO removes the shift registers used in the conventional DLDO. It achieves a transient speed improvement in the ns range and a quiescent current reduction by 9X over the conventional DLDO design that targets μA load current. The RLC-DLDO has an input voltage range between 0.8V and 0.6V and generates an output voltage range between 0.7V to 0.5V for load current between 10μA and 500μA. The design is implemented in 22nm FDSOI and occupies an active area of 0.0171mm2. The simulation results show that the peak efficiency is 99.9% and the load transient response time is 5ns at VL=0.5V.

View full paper and presentation here: https://ieeexplore-ieee-org.libconnect.ku.ac.ae/document/9181174

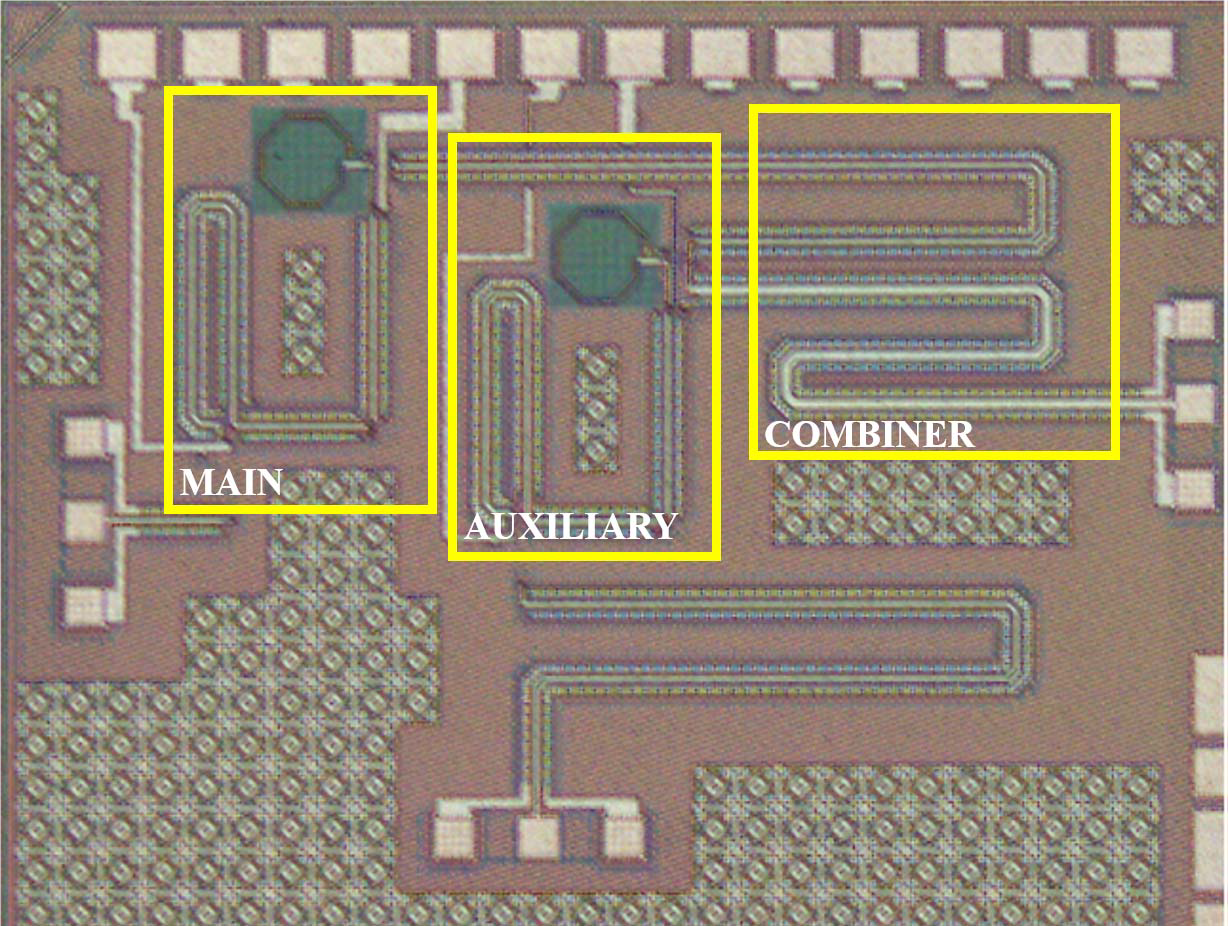

A 28GHz, Modified Doherty Power Amplifier (MDPA) was implemented in 22nm FDSOI CMOS technology from GF. The MDPA adopts an asymmetrical topology utilizing two cascode CMOS amplifiers as the main (Class-A) and auxiliary (Class-C). This allows a supply voltage of 2.5V and consequently higher output power. The use of a main Class-A amplifier is conducive to a higher linearity (IIP3). The integrated design implements the main and auxiliary amplifier, along with the matching and transmission line networks on chip. The fabricated amplifier occupies an area of 1.2mm 2 , exhibits 12 dBm saturated output power, a peak power gain of 10dB, 16% peak power-added efficiency (PAE) and 12.5% at 6-dB back-off. The measured IIP3 is 20dBm.

View full paper and presentation here: https://ieeexplore-ieee-org.libconnect.ku.ac.ae/document/9180851