Ratioed Logic Comparator Based Digital LDO Regulator in 22nm FDSOI: presented in 2020 IEEE International Symposium on Circuits and Systems (ISCAS) by Dr. Dima Kilani

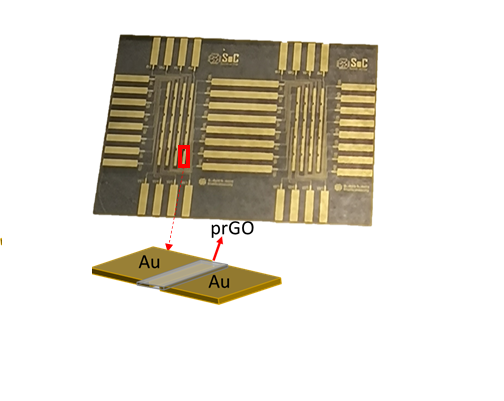

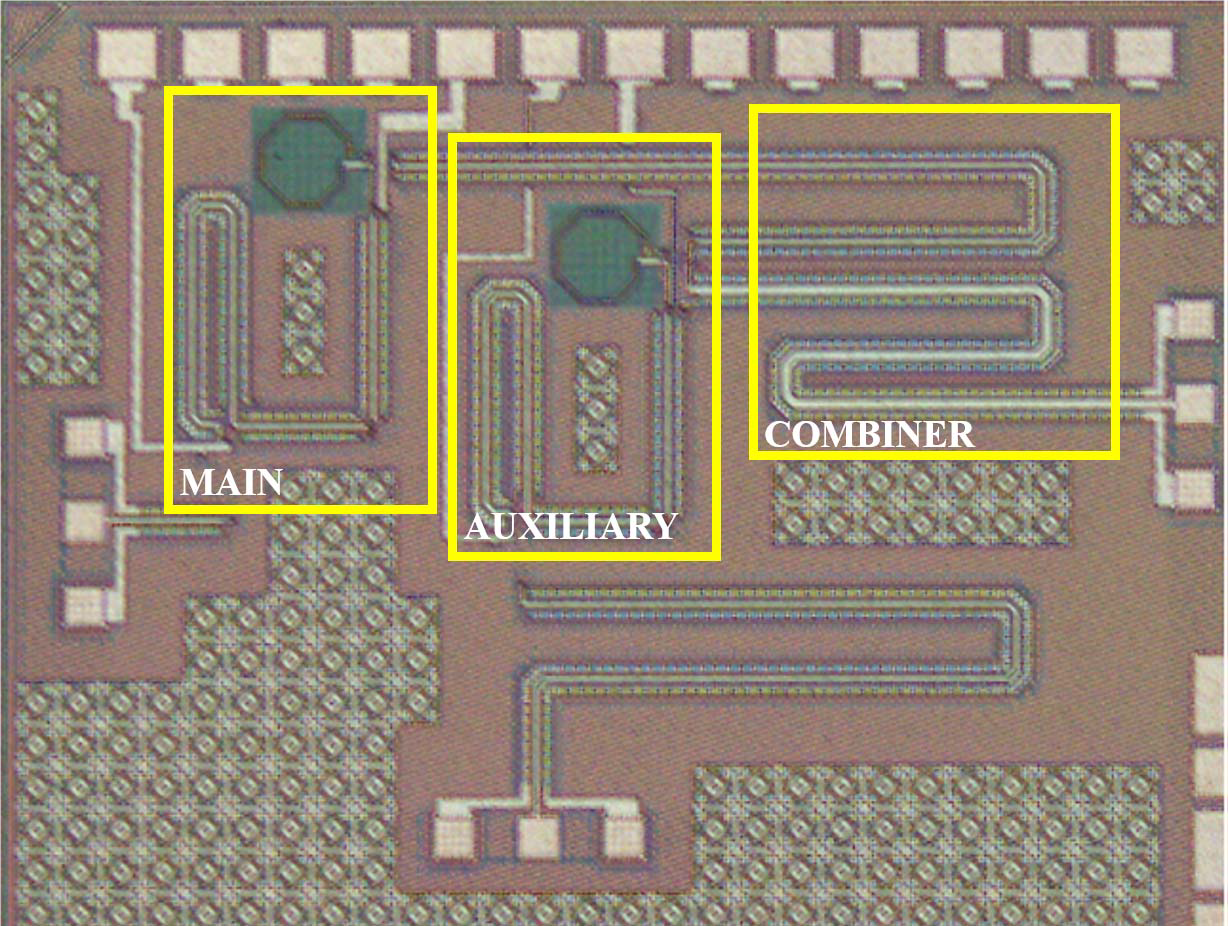

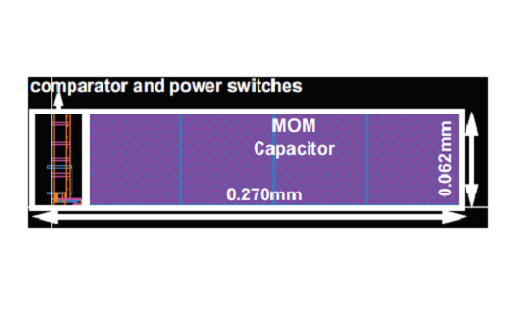

This paper presents a fast and an efficient digital LDO (DLDO) regulator utilizing a clock-less ratioed logic comparator (RLC). In addition to eliminating the clock, the proposed RLC-DLDO removes the shift registers used in the conventional DLDO. It achieves a transient speed improvement in the ns range and a quiescent current reduction by 9X over the conventional DLDO design that targets μA load current. The RLC-DLDO has an input voltage range between 0.8V and 0.6V and generates an output voltage range between 0.7V to 0.5V for load current between 10μA and 500μA. The design is implemented in 22nm FDSOI and occupies an active area of 0.0171mm2. The simulation results show that the peak efficiency is 99.9% and the load transient response time is 5ns at VL=0.5V.

View full paper and presentation here: https://ieeexplore-ieee-org.libconnect.ku.ac.ae/document/9181174